Każdy z producentów stosuje własne rozwiązania w zakresie architektury 3D NAND Flash, w celu stworzenia jak najmniejszej i zaraz najpojemniejszej kości pamięci. Począwszy od skalowania logicznego, tj. zwiększania bitów przypadających na jedną komórkę, przez skalowanie fizyczne komórek NAND i całych układów, koncentrując się na proporcjonalnym zmniejszeniu wymiarów „xyz”, odnosząc się do kartezjańskiego układu współrzędnych. Niestety dość często zdarza się, że w wielu newsach branżowych, w których opisywane są świeże dokonania w zakresie produkcji innowacyjnych rozwiązań 3D NAND, autorzy tych krótkich publikacji jedynie lakonicznie napominają o przyjętej architekturze całego chipu, a szkoda.

Przyjrzyjmy się zatem aktualnie stosowanym rozwiązaniom w zakresie projektowania chipów NAND 3D TLC. Zacznijmy jednak od przypomnienia kilku kluczowych pojęć niezbędnych do zrozumienia dalszej części materiału.

Obwody peryferyjne – są to wytworzone w technologii CMOS (Complementary Metal Oxide Semiconductor) peryferyjne elementy układu NAND, zaliczyć do nich można: bufory stron, wzmacniacze, pompy ładunku, układy kontroli etc.

Macierz komórkowa NAND – wielowarstwowa struktura komórek pamięci tworzona przez ułożone w porządku wertykalnym tranzystory [1].

Podłoże – obszar krzemu, w którym występuje niedobór elektronów (typ p) lub ich nadwyżka (typ n).

Aktualnie na rynku stosowane są trzy rozwiązania dotyczące aranżacji architektury układów 3D NAND Flash.

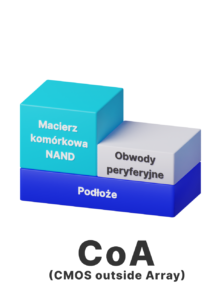

Pierwsze to CMOS outside wafer (CoA), w którym układy tranzystorowe lokowane są obok bloku z komórkami NAND. Obie sekcje posadowione są na podłożu przewodzącym. Jest to pierwsza chronologicznie technologia zaprezentowana w 2016 roku. Aktualnie jest sukcesywnie zastępowana przez dwie kolejne opisane poniżej. Powód jej stopniowego wycofywania jest zauważalny gołym okiem. Powierzchnia całego „stacku” NAND w wymiarach x i y jest zbyt duża, jeśli porównamy ją z wymiarami, które mogą dać nam następne dwie technologie – CuA i CBA (WoW). Wymiary podstawy komórki są zwyczajnie zbyt duże i takie podejście nie współgra z tendencją dążącą do minimalizacji całego układu w celu efektywniejszego zagospodarowania płytki PCBA chipami.

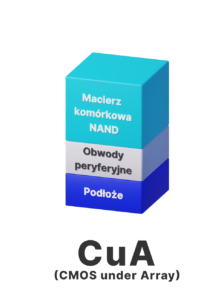

Drugim rozwiązaniem jest CMOS under array (CuA) lub PuC [2] (Hynix) – tutaj podłoże wraz z CMOS są pozycjonowane pod macierzą NAND. Dzięki temu podejściu podstawa modułu (wymiary x i y) są wyraźnie mniejsze, przez co możliwa jest implementacja większej ilości kości na płytkę PCBA urządzenia. [3] Architektura CuA jest teraz najpopularniejszym podejściem do projektowania układów 3D NAND wśród producentów.

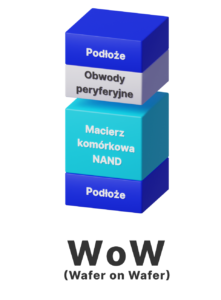

Trzecim, najmłodszym technologicznie rozwiązaniem, jest WoW – Wafer on Wafer (Xtacking –YMTC [4]) lub CBA (CMOS Bonded Array – Kioxia/WD [5]), w którym litografie układów CMOS oraz komórek NAND lokowane są na osobnych waferach i łączone w procesie technologicznym zwanym „wafer bonding”. Na razie technologia ta nie została jeszcze zaimplementowana do układów przemysłowych 3D NAND.

Jak już zostało wspomniane wcześniej, technologia CoA nie jest już głównym rozwiązaniem optymalizującym wielkość kości 3D NAND. Producenci skupiają się na architekturach CuA i CBA (WoW). Należy zaznaczyć, że nie są to rozwiązania idealne, przez co pomimo wielu wyraźnych zalet, mają również swoje ograniczenia.

CMOS Under Wafer jest bez wątpienia solucją korzystniejszą pod kątem ekonomicznym, ponieważ do stworzenia kości NAND w tej technologii wystarczy jeden wafer. Z kolei produkcja zgodnie z założeniami CMOS Bonded Array (lub Wafer on Wafer) pociąga za sobą większe koszty, gdyż wymaga ona zastosowania dwóch wafli krzemowych – jednego pod litografię CMOS, drugiego dla komórek NAND.

Z drugiej strony taka technologiczna „kanapka” ma istotną zaletę: dzięki oddzieleniu CMOS od NAND skutecznie odprowadza się ciepło, przez co jakość CMOS kości NAND nie ulega pogorszeniu i cały układ może uzyskiwać lepsze wyniki prędkości I/O. [6]

Konkludując, należy mieć na uwadze, że wybór typu odpowiednich modułów 3D NAND Flash do urządzenia, nie zawsze realizowany jest na podstawie oceny gotowego materiału, ale w oparciu o przyjętą metodę jego produkcji. Dlatego w Goodram Industrial przywiązujemy dużą wagę do weryfikacji możliwości technologicznych naszych dostawców i dobieramy ich komponenty, uwzględniając wymagania aplikacji docelowej. Aktualnie, nasze rozwiązania przemysłowe SSD bazują na kościach 3D TLC wykonanych w przodującej technologii – CuA.

Źródła:

[1] https://goodram-industrial.com/technologia/metody-detekcji-i-korekcji-bledow-w-pamieciach-masowych/

[2] https://news.skhynix.com/nand-development-history/

[3] https://www.mdpi.com/2079-9292/10/24/3156

[4] https://www.ymtc.com/en/technicalintroduction.html

[5] https://apac.kioxia.com/en-apac/business/news/2023/20230330-1.html

[6] https://www.nxtbook.com/nxtbooks/ieee/mssc_fall2020/index.php?startid=58#/p/58