Each manufacturer applies its own solutions to the 3D NAND Flash architecture, with the aim of creating the smallest and immediately most capacious memory bone possible. These range from logical scaling, i.e. increasing the bits per cell, to physical scaling of NAND cells and entire chips, focusing on proportionally reducing the ‘xyz’ dimensions, referring to the Cartesian coordinate system. Unfortunately, it is quite common that in many industry news stories describing fresh developments in the production of innovative 3D NAND solutions, the authors of these short publications only laconically hint at the overall chip architecture adopted, which is a pity.

Let us therefore take a look at the current developments in 3D TLC NAND chip design. However, let’s start with a reminder of some key concepts necessary to understand the rest of the material.

Peripheral circuits – These are the CMOS (Complementary Metal Oxide Semiconductor) peripheral components of a NAND chip, and include page buffers, amplifiers, charge pumps, control circuits, etc.

NAND cell matrix – a multilayer structure of memory cells formed by transistors arranged in vertical order [1].

Substrate – an area of silicon in which there is a deficiency of electrons (p-type) or a surplus of electrons (n-type).

There are currently three solutions on the market for arranging the 3D NAND Flash chip architecture.

The first is the CMOS outside wafer (CoA), in which the transistor chips are located next to a block with NAND cells. Both sections sit on a conductive substrate. This is the first chronological technology presented in 2016. It is currently being successively replaced by two others described below. The reason for its gradual withdrawal is noticeable to the naked eye. The area of the entire NAND ‘stack’ in x and y dimensions is too large when compared to the dimensions that the next two technologies, CuA and CBA (WoW), can give us. The dimensions of the cell base are simply too large and this approach does not harmonise with the trend towards minimisation of the whole chip in order to use the PCBA board more efficiently with chips.

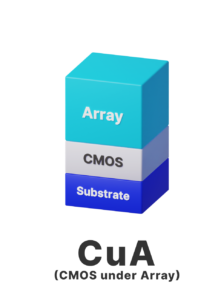

The second solution is the CMOS under array (CuA) or PuC [2] (Hynix) – here the substrate together with the CMOS are positioned under the NAND array. With this approach, the module base (x and y dimensions) is noticeably smaller, making it possible to implement more dice on the device PCBA. [3] The CuA architecture is now the most popular approach to 3D NAND chip design among manufacturers.

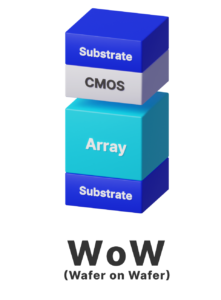

The third, and technologically newest, solution is WoW – Wafer on Wafer (Xtacking -YMTC [4]) or CBA (CMOS Bonded Array – Kioxia/WD [5]), in which the lithographs of CMOS chips and NAND cells are located on separate wafers and bonded together in a process called ‘wafer bonding’. So far, this technology has not yet been implemented in industrial 3D NAND chips.

As mentioned earlier, CoA technology is no longer the mainstream solution for optimising the size of 3D NAND dice. Manufacturers are focusing on CuA and CBA (WoW) architectures. It should be noted that these are not ideal solutions and thus, despite their many clear advantages, also have their limitations.

CMOS Under Wafer is undoubtedly the more economically advantageous solucition, as a single wafer is sufficient to create NAND dice using this technology. On the other hand, manufacturing according to the CMOS Bonded Array (or Wafer on Wafer) approach entails higher costs, as it requires two silicon wafers – one for CMOS lithography and the other for NAND cells.

On the other hand, such a technological ‘sandwich’ has an important advantage: by separating the CMOS from the NAND, heat is effectively dissipated, so that the CMOS quality of the NAND dice is not degraded and the whole chip can achieve better I/O speed performance.” [6]

In conclusion, it is important to bear in mind that the selection of the type of suitable 3D NAND Flash modules for a device, is not always carried out on the basis of the evaluation of the finished material, but on the basis of the production method adopted. Therefore, at Goodram Industrial, we attach great importance to verifying the technological capabilities of our suppliers and select their components taking into account the requirements of the target application. Currently, our industrial SSD solutions are based on 3D TLC dice made with the leading technology – CuA.

Sources:

[1] https://goodram-industrial.com/technologia/metody-detekcji-i-korekcji-bledow-w-pamieciach-masowych/

[2] https://news.skhynix.com/nand-development-history/

[3] https://www.mdpi.com/2079-9292/10/24/3156

[4] https://www.ymtc.com/en/technicalintroduction.html

[5] https://apac.kioxia.com/en-apac/business/news/2023/20230330-1.html

[6] https://www.nxtbook.com/nxtbooks/ieee/mssc_fall2020/index.php?startid=58#/p/58